FPGA Architect

FPGA ArchitectTM is a design automation platform for generating correct-by-construction embedded FPGA cores.

Value Proposition

Developing an FPGA from scratch is a complex engineering endeavor that demands a large team of experts in FPGA design, EDA tools, circuit optimization, and physical design. Even porting an existing FPGA architecture to a new process node can take years and cost millions. To lower the barrier to custom FPGA development, Zero ASIC has created a suite of FPGA generator tools that dramatically reduce the engineering effort, cutting development time and cost by an order of magnitude.

Overview

Leveraging high level Python based FPGA architecture definitions and an automated standard cell back-end implementation engine, FPGA Architect automates the generation of:

- Verilog RTL and netlists

- Hardened array layout macros (DEF/GDS)

- Architecture files for Logik

- Testing and integration infrastructure

Key FPGA Architect features:

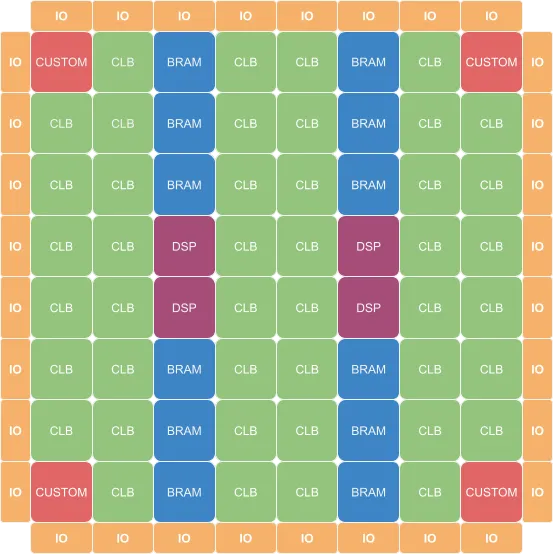

- Composition of homogeneous FPGAs (LUT only)

- Composition of heterogeneous FPGAs (LUTs + DSPs + BRAM)

- Support for integrating custom hard macros within fabric

The following table shows the range of FPGA Architect parameters that have been thoroughly tested. More architecture options are under development.

| Architecture Option | Min | Max |

|---|---|---|

| Array size | 3 x 3 | 128 x 128 |

| LUT size | 4 | 6 |

| Fracturable LUTs | None | 2-way |

| LUTs per CLB | 2 | 10 |

| I/Os per IO block | 1 | 16 |

| Clock Domains | 1 | 4 |

| CLB Crossbar connectivity | 45% | 100% |

| Switch box connectivy | 12.5% | 25% |

| Routing Channels | 32 | 200 |

Target Markets

- Aerospace and Defense

- Manufacturing

- Automotive

- Wireless infrastructure

- Networking

- Robotics

- Test and Measurement

- Consumer Electronics

- High Performance Computing

Access Model

FPGA Architect is accessible on a per project basis from Zero ASIC. Contact our development team to learn more about the engagement model and process availability.